在当今信息技术飞速发展的时代,集成电路(IC)作为电子设备的核心,其制造过程融合了物理、化学、材料科学和计算机科学的尖端成果。而将一颗复杂的芯片从设计图纸变为现实中的硅片,不仅依赖于精密的制造工艺,更离不开可制造性设计(DFM)和专用软件开发的协同支撑。这三者构成了现代集成电路产业密不可分的三驾马车,共同驱动着摩尔定律的延续与技术创新的步伐。

一、 集成电路制造工艺:从图纸到硅片的精密雕刻

集成电路制造工艺,俗称“制程”,是指将电路设计通过一系列复杂、精密的物理和化学步骤,在半导体晶圆上实现的过程。其主要流程包括:

- 晶圆制备:以高纯度的单晶硅为原料,通过拉伸、切割、抛光等步骤,制备出表面近乎完美的晶圆。

- 薄膜沉积:在晶圆表面生长或沉积各种材料的薄膜,如二氧化硅(SiO₂)、多晶硅、金属等,作为后续加工的基底。

- 光刻:这是整个工艺的核心。利用光刻胶和特定波长的光源(如深紫外DUV、极紫外EUV),通过掩模版将电路图案精确地“投影”到晶圆上。其分辨率直接决定了芯片上晶体管的最小尺寸(如7纳米、5纳米)。

- 刻蚀:将光刻后显现出来的图案,通过干法(等离子体)或湿法(化学溶液)刻蚀,转移到下方的薄膜或硅基底上。

- 离子注入与扩散:向硅中注入特定的杂质原子(掺杂),以形成晶体管所需的P区和N区,从而构建出MOSFET等核心器件。

- 化学机械抛光(CMP):平坦化晶圆表面,为后续添加新的金属互联层做好准备。

- 金属化与互连:通过沉积和刻蚀形成多层金属导线(通常为铜),将数以亿计的晶体管连接起来,构成完整的电路。

随着工艺节点不断微缩(进入纳米尺度),制造过程面临着物理极限、量子效应、工艺变异等前所未有的挑战,这使得单纯依靠工艺技术的进步变得愈发艰难。

二、 可制造性设计(DFM):连接设计与制造的桥梁

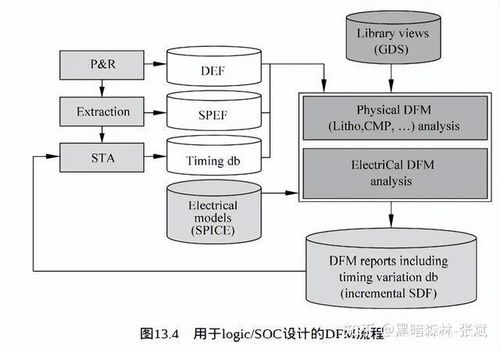

可制造性设计(Design for Manufacturability, DFM)正是在此背景下应运而生并日益重要的理念与方法。它要求在芯片设计阶段,就提前考虑和规避制造工艺中可能遇到的各种问题与限制,从而提高设计在现有工艺下的良率、可靠性和性能。DFM的核心目标是从“设计正确”走向“设计易于制造且高产”。其主要技术范畴包括:

- 设计规则检查(DRC)的演进:从简单的几何间距检查,发展到包含复杂的光学邻近效应修正(OPC)规则、多重曝光规则等,确保设计图形在经过光刻等物理过程后仍能保持原貌。

- 工艺仿真与建模:建立精确的工艺模型(如光刻仿真、刻蚀仿真、CMP仿真),在设计阶段预测制造后的实际形状和电学参数,识别潜在热点(Hot Spot)。

- 良率导向设计(DFY):通过添加冗余结构(如备用电路)、优化布局以减少对工艺变异的敏感性、采用更稳健的电路架构等手段,主动提升芯片的预期良率。

- 统计时序分析:考虑到工艺参数(如晶体管阈值电压、导线宽度)在晶圆内和晶圆间的波动(工艺角),进行统计分析,确保芯片在所有变异情况下都能满足时序要求。

DFM的本质是让设计与工艺实现“对话”,将制造知识前馈至设计端,从而减少试错成本,加速产品上市时间。

三、 软件开发:赋能设计与制造的智能引擎

无论是复杂的芯片设计,还是精密的工艺控制与DFM实施,都离不开强大软件工具的支撑。相关的软件开发构成了集成电路产业的“软实力”基础。

- 电子设计自动化(EDA)软件:这是芯片设计的核心工具链,涵盖了从系统架构、逻辑综合、电路仿真、物理布局布线到版图验证的全流程。EDA软件集成了大量的DFM功能和工艺设计套件(PDK),是设计师将创意转化为可制造版图的关键平台。

- 工艺仿真与计算光刻软件:用于模拟光刻、刻蚀等物理过程,并生成用于OPC和反向光刻技术(ILT)的复杂掩模版图形。随着EUV光刻的应用,相关软件的算法复杂度和计算需求呈指数级增长。

- 制造执行系统(MES)与良率管理系统(YMS):在晶圆厂中,软件负责管理生产流程、跟踪每一片晶圆的状态、控制设备参数、收集海量生产数据,并通过数据分析(常结合机器学习)来诊断缺陷根源、持续优化工艺、提升良率。

- TCAD(技术计算机辅助设计)软件:用于模拟半导体器件的物理特性,帮助工艺工程师开发新的器件结构和工艺模块。

当前,人工智能与机器学习正在深度融入这些软件工具中,用于更快的设计空间探索、更精准的工艺模型校准、更智能的缺陷分类和预测性维护,进一步推动产业向智能化方向发展。

结论

集成电路制造工艺、可制造性设计与软件开发三者之间形成了紧密的闭环。先进的制造工艺为芯片性能提升提供了物理可能;可制造性设计确保了这种可能性能够高效、稳定地转化为现实产品;而贯穿始终的软件开发则为前两者提供了实现、优化和创新的智能工具与平台。三者协同演进,共同应对着后摩尔时代的技术挑战,不断拓展集成电路技术的边界,支撑起从智能手机、云计算到人工智能和自动驾驶的广阔数字世界。